# Full Bridge Phase Shifted On-Chip Dc-Dc Converter For Point-Of-Load Voltage Regulation

Jaya Kaviya. V., Manjula Devi . K., Dr. Marimuthu. C. N

PG student, Dept. of electronics and communication engineering, Nandha Engineering College, Erode-638052, Tamilnadu, India Project Guide, Dept. of electronics and communication engineering, Nandha Engineering College, Erode-638052, Tamilnadu, India

Project Guide, Dept. of electronics and communication engineering, Nandha Engineering College, Erode-638052, Tamilnadu, India

Email: jayavasu1991@gmail.com

ABSTRACT: DC-DC converter is important in portable electronic devices which are supplied with power from batteries primarily. Such electronic devices often contain several sub-circuits, in which switched DC to DC converters offer a multiple voltage levels from a partially lowered battery voltage thereby saving space instead of using multiple batteries. An active filter based on-chip DC-DC voltage converter provides distributed multiple local power supplies across an integrated circuit while maintaining high current efficiency within a small area. The area occupied by the circuit is small because no inductor or capacitor is required than other voltage regulators. The circuit is appropriate for noise sensitive portions of an integrated circuit. Digital current mode control in a full bridge phase shifted DC-DC converter is introduced. So that, the digital current controller performs gain adjustments scheme to achieve fast dynamic response and a current sampling scheme to avoid switching noise and spike in DC-DC converter. The MATLAB tool is used for the simulation of the voltage regulators

**Keywords:** Hybrid voltage regulator, active filter, On-Chip voltage regulator, full bridge phase shifter, point –of –load voltage regulation.

### 1 INTRODUCTION

In recent years, there is an impressive growth in personal computing devices and wireless communication systems. This was the main reason that the VLSI designers take into consideration of power consumption in addition to area and throughput. It is clear that in the absence of lowpower design techniques such devices will suffer from either a short operation battery life or a very heavy battery packup. Moreover, there are also some very important concepts such as reliability, hot spot detection, electromigration and packing selection which make the power consumption a major concern in VLSI design. The lower interests are driven both by evolutionary and revolutionary trends. It is estimated that in the next seven years about 50% of the electronic market will be in the portable system, while keeping the heat generation under the control to avoid forced cooling. The low power requirement needs solution. The solutions are supply and demand. On the supply side we need better denser and smarter batteries with efficient power conversion and regulation, improved heat dissipation, distribution and cooling techniques. On the other hand low power is obtained by better process and efficient computation technique. The power supply voltage aggressively scales with each technology generation, making the delivery of a high quality supply voltage to noise sensitive circuit blocks is highly challenging. The number of voltage domains within an integrated circuit is increasing to satisfy stringent power budgets. The increase in the number of voltage domains requires new techniques to generate these voltages close to the load circuitry while occupying a small area. The power savings is greater when the voltage regulators are close to the load devices (Point-of-load voltage regulation). Size is the primary issue for point-of-load voltage regulation. DC-DC voltage converters are used as on-chip

power supplies in high performance integrated circuits. The DC-DC voltage converters designed should be capable of distributing multiple local power supplies across an integrated circuit. The primary issue in the design of a conventional on-chip voltage converter is the physical area. To produce a voltage regulator appropriate for distributed point-of-load voltage regulation, the passive LC filter within the buck converter is replaced with a more area efficient active filter circuit. Hence an active filter based on-chip DC-DC voltage converter is used for point-of-load voltage regulation. The converter uses filter structure and switching input voltage to produce the desired output voltage within a small area. Due to the on-chip voltage converter which placed close to the load device the major issue of parasitic impedance of the power distribution network is reduced. At high frequencies, square wave converters' switching losses become very high leading to excessive heat dissipation. Even if the increased switching frequency does not cause unacceptable switching losses, the oscillations caused by converter parasitic elements may cause high current and voltage stresses, which are almost unpredictable, depending on circuit layout. The zero-voltage transition approach, as well as the active-clamp snubber approach, leads to zero-voltage switching of the transistors and zerocurrent switching of the diodes.

### 2 SHORT HISTORY OF VOLTAGE REGULATOR

Voltage regulators are used to produce regulated output from the unregulated input voltage. Different types of voltage regulators are available they may be linear, switched and switched capacitor. The linear DC-DC converter can output at lower voltage from the input voltage. Linear regulator responds faster than the switching regulator to changes in the unregulated supply voltage and

load current[2],[4]. Output voltage ripple and noise is lower than the switching voltage regulator. But this converter is not suitable for large drop and high current application Switched DC-DC converter converts one voltage level is converted to another voltage level by storing the energy and releasing the energy at different voltage. This is achieved by using switched-mode, or, chopper circuits whose elements dissipate less power. Pulse-width modulation allows control and regulation of the total output voltage. In this device a power switch is used which is turned on by a pulse fed at its gate terminal. MOSFETS is used as a switching device because the frequency used is high thereby reducing the size of the filter. This converter can be implemented in non-isolated or isolated. Further each topology contains a hard switch and resonant circuit. There different types of switched converters they may be buck converter used to step down the input voltage and boost converter used to step up the input voltage level. Switched capacitor is achieved by alternatively connecting capacitors in input and output in different topologies. The operation is two capacitor is charged in series and discharges in parallel. This produces the output half the input voltage. This type of converter is large voltage application where the magnetic element may get damaged. Though it is suitable for high voltage application there is a disadvantage that the resistive switches dissipate more power.

### 3 DESIGN CONSIDERATIONS FOR VOLTAGE REGULATOR

Many factors must be considered when designing a voltage regulator. Minimizing power consumption is always desirable, particularly with portable consumer electronics. Less power consumption allows the device's battery to last longer. And the related factor is efficiency, which is determined by the dropout voltage. Dropout voltage is defined as the difference between the unregulated supply voltage and regulated supply voltage. Lowering the dropout voltage can lower the voltage of the unregulated power supply, and this in turn lowers the power consumption of the regulator. A less power hungry device may also use a smaller battery, leading to better portability. Decreasing the area of a voltage regulator also improves portability. A device that uses several voltage regulators benefits greatly from a voltage regulator design that takes up minimal area, because the structure that houses the circuitry can be made smaller and hence easier to carry around. Smaller area also means that more devices will fit onto one wafer, decreasing the cost of manufacturing. Bandwidth is another important specification in voltage regulator design. The higher the bandwidth of a regulator, the more quickly it can react to changes in input and power supply and keep the output voltage constant. While designing the voltage regulator, if the bandwidth is high the performance of the regulator is improved. High bandwidth also improves the power supply rejection ratio (PSRR) of the regulator, which is a measure of how well the regulator attenuates noise on the power supply. The better the power supply rejection, the less the output voltage changes in response to fluctuations in the supply. The PSRR can be characterized by the magnitude of attenuation as well as the range of frequencies over which the attenuation occurs. Usually PSRR is greatest at low frequencies and rolls off as the frequency increases. Yet another factor to consider in voltage regulator design is stability. Since the purpose of a voltage regulator is to provide a steady voltage to other components, a regulator prone to oscillation is not desirable. Since stability varies with load conditions, which may be incompletely specified or unknown, a regulator design that has good phase margin for a wide range of output loads is best. Associated with stability is load regulation, the percentage change in output voltage in response to a change in the output. The importance of the numerous voltage regulator specifications vary widely depending on the application.

## 4 OVERVIEW OF THE HYBRID VOLTAGE REGULATOR

An essential part of distributing power from a DC supply to its points of load (POLs), has typically been implemented with a PWM circuit. However a couple of factors have applied increasing pressure to regulator design. Firstly, power density is being forced up continuously. Secondly, DC power supply voltage levels are tending to rise to minimize distribution losses, while device voltages are reducing to increase internal speed and efficiency. These trends combine to increase the voltage drop and associated switching losses across the regulator. The focus is mainly on power savings in VLSI technology. The power savings will be greater when the voltage regulators are close to the load devices that is point-of-load voltage regulation. The primary issue in the point-of-voltage regulator is the size of regulator. Several topologies proposed for reducing the size of the voltage regulator to make the design suitable point-of -load voltage regulation [9]. DC-DC converters are generally used as On-Chip power supplies in high performance integrated circuits. An ultra small area efficient voltage converter is required for the next generation of multivoltage systems because previous systems are highly sensitive to (P/G) noise[1]. Buck converters, which are stepdown switching DC-DC converter, are popular because of their high power efficiency [16]-[18]. A second order inductor-capacitor (LC) passive filter in a buck converter occupy significant On-Chip area, therefore the passive components have been implemented off-chip. As a consequence of placing these components off-chip, significant voltage drop, power loss and degradation in speed and accuracy of the load regulation occurs and as a result causing slow response times and changing output levels. An On-Chip passive LC filter is therefore infeasible due to the large area when multiple On-Chip voltage regulators are needed[12]. To produce a voltage regulator appropriate for distributed point-of-load voltage generation, the passive LC filter within a buck converter is replaced with a more area efficient active filter circuit [11]. A switching input voltage is used to generate the desired output voltage, and the converter uses a filter structure to produce the desired output signal. The current supplied to the output node, however, does not originate from the input switching signal, rather it originates from the operational amplifier (Op Amp) output stage, similar to a linear voltage converter. The proposed voltage converter is therefore a hybrid combination of a switching and linear DC-DC converter [1]

#### 5 HYYBRID VOLTAGE REGULATOR DESIGN

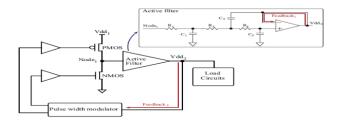

Conventional buck converter steps down the applied input voltage to obtain the required output voltage [1] are shown

in Fig 1. But the area occupied by the converter is large due to the size of the inductor is large and when the inductor is placed off-chip the area reduces but the power loss and parasitic loss occurs[6]. For low power and area efficient application the conventional buck converter is not suitable. Hence an active filter based DC-DC converter is designed as shown in Fig 2.

Fig 2. Hybrid Voltage Regulator

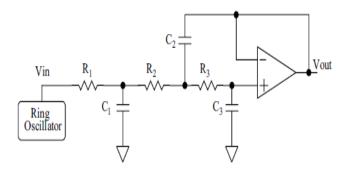

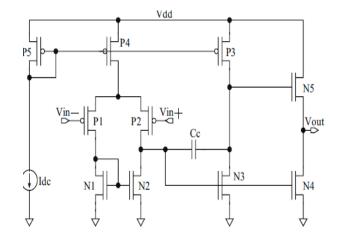

For obtaining small area the LC bulky circuit is replaced by active filter. Buffers size depends on the circuit that deliver the current to the load in buck transistor deliver the current to the load hence large buffers used but in hybrid voltage regulator small buffers are used because current delivered to the is by op-amp [1]. Feedback is necessary to produce line and regulation. Active filter structure has a feedback loop. So, the area occupied is small and power dissipation is also reduced. Many design consideration are included in active filter design and op-amp design. For a voltage regulator, the on-chip area requirement, the power dissipated by the active components should be low. Two topologies are popular for implementing an integrated low pass filter active filter, i.e., multiple feedback and sallenkey [16]. Multiple feedback low pass filters use capacitive and resistive feedback within the feedback path from the output to the input. A dc current path exists in the resistive feedback hence power dissipation increases. Alternatively, sallen-key low pass filter use only capacitive feedback, the power dissipation is less than the multiple feedback topology because there exists no direct DC path. Filter structure may be butterworth or chebyshev, chebyshev filter structure is chosen to avoid resistive components connected to ground to produce finite zeros A third order low pass unity gain sallen-key filter topology is shown in Fig 3 [18].Gain-bandwidth product and power loss depends on the op-amp structure within the active filter [1]. Three stage differential- input single ended cmos op-amp filter structure is used in hybrid regulator is shown in the Fig 4.

Fig 3. Active filter structure

Fig 4 .Three stage differential single ended op-amp structure

### 6 FULL BRIDGE PHASE SHIFTED VOLTAGE REGULATOR

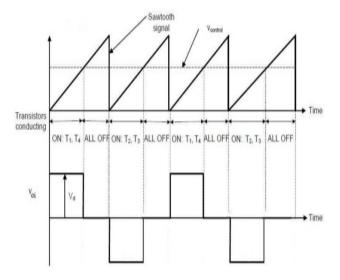

High-density PWM regulators have evolved with improved IC integration, MOSFETs and packaging, their design is no longer sufficient to meet the power demands they face. This is mainly due to switching losses within the regulator MOSFETs. These must be overcome or avoided to achieve any significant boost to regulator performance. A better solution uses Zero Voltage Switching (ZVS) topology, which allows for operation at a higher frequency and at higher input voltages without sacrificing efficiency. Phase shifted full bridge topology is used to achieve ZVT. In the conventional circuit, as Q1 is turned on and Q2 turned off, a very high current flows through the MOSFET pair, since Q2's body diode appears as a short circuit during its reverse recovery time. Other losses arise due to discharging Q1's output capacitance, and to reverse recovery in Q2. These losses increase as the switching frequency or input voltage increases. By contrast the ZVS design addresses the high turn-on losses of the conventional regulator by eliminating high current body diode conduction prior to turn on of the high side MOSFET. bringing the D-S voltage of the high side MOSFET to zero or nearly zero and producing no high current spikes or damaging ringing. The ZVS action applied to Q1 removes its Miller effect at turn on, allowing the use of a smaller driver and lower gate drive [20]. The switching topology used for the full-bridge converter is the bipolar voltage switching, where the transistors are switched in pairs. Transistors T1 and T4 are considered as one switch pair and transistors T2 and T3 are considered as the other switch pair. The output voltage V0 is controlled and regulated by the PWM scheme seen in Figure 5 where a sawtooth signal is compared with a voltage control signal from the control circuit. During the first half period, the switchpair T1 and T4 are conducting as long as the sawtooth signal is lower than the control signal. When it exceeds the control signal the transistors stops to conduct until the second half period takes place when the switchpair T2 and T3 starts to conduct until the sawtooth signal yet again exceeds the control signal. This procedure repeats itself from period to period Another type of control is the phase-shift control which provides a convenient method for achieving zero voltage switching, significantly reducing

the switching losses. Stored energy is then used to charge and discharge bridge switch capacitance during a freewheeling stage created by phase shifting the ON times of opposite pairs of transistors in the bridge configuration. These provide regulation at a higher efficiency and from a smaller form factor than achievable from conventional hard switching, high density regulators.

Fig 5 Full Bridge Converter Switching Topology

#### 7 SYSTEM COMPARISON

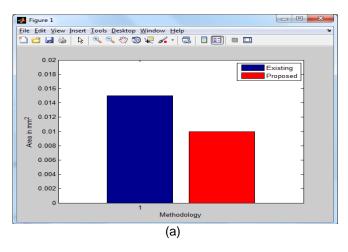

The Fig 5 shows performance comparison parameter among different DC-DC converter. From the Fig 5 it indicates that the Full Bridge Phase Shifter voltage converter is better than the Hybrid voltage regulator.

Fig 5 comparison between hybrid and full bridge phase shifter regulator (a) area

Table 1 Comparison table

|                   | HYBRID   | FULL<br>BRIDGE<br>PHASE<br>SHIFTED |

|-------------------|----------|------------------------------------|

| DELAY             | 10ms     | 8ms                                |

| OUTPUT<br>VOLTAGE | 0.5-1    | 0.9                                |

| INPUT<br>VOLTAGE  | 0.75-1.2 | 1.8                                |

### **8 RESULTS AND DISCUSSION**

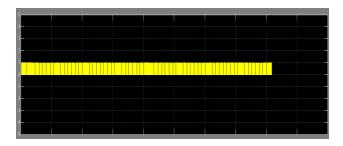

Based on the generated duty cycle output of the generated voltage is regulated. Hence regulated output voltage occurs at the load. MOSFET1 and MOSFET2 are the switching device. Feedback controller is the PWM generator. Pulse width modulator output waveform is shown in Fig 6.

Fig 6 Output waveform of PWM.

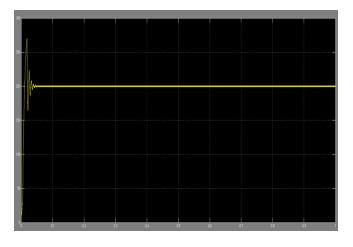

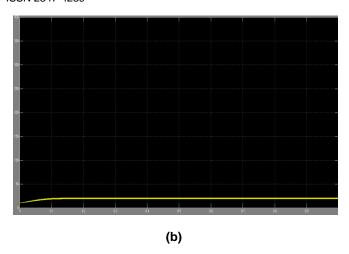

Fig 7 output voltage waveform. (a)Output voltage for hybrid regulator, (b) output voltage for full bridge phase shifter

#### 9 CONCLUSION

A full bridge phase shifted DC-DC converter power supply is appropriate for point-of -load voltage regulation is proposed. The on-chip area of the proposed DC-DC converter is lower than the proposed state of art. The need for an off-chip capacitor or advanced on-chip compensation technique to satisfy stability and performance requirements is eliminated in the proposed circuit. This circuit therefore provides a means for distributing multiple power supplies close to the load to reduce power/ground noise while enhancing circuit performance by delivering a high quality supply voltage to the load circuitry. With the proposed voltage regulator, on-chip signal and power integrity is significantly enhanced while providing capability for distributing multiple point-of-load voltage regulation. Phase shifted PWM generator produces programmable phase shifted PWM signals and a gain adjustment scheme is applied to adjust the controller parameters of digital controller to obtain fast dynamic response. Synchronous current sampling scheme is applied to avoid the switching noise and spike in the output of On-Chip DC-DC converter.

### 9 REFERENCES

- [1] Selcuk Kose, Sally Pinzon, Bruce McDermott, and Eby Friedman.G, (2013), "Active filter based hybrid on-chip DC-DC converter for point-of-load voltage regulation".

- [2] Al-Shyoukh. A, Lee. H, and Perez. R, (2007), "A transient-enhanced low quiescent current low-dropout regulator with buffer impedance attenuation," IEEE J. Solid-State Circuits, vol. 42, no. 8, pp. 1732–1742.

- [3] Besten.G. W. D and Nauta. B, (1998), "Embedded 5 V-to-3.3 V voltage regulator for supplying digital IC's in 3.3 V CMOS technology," IEEE J. Solid-State Circuits, vol. 33, no. 7, pp. 956–962.

- [4] Guo. J and Leung. K. N, (2010), "A 6-μW chiparea-efficient output capacitorless LDO in 90-nm CMOS technology," IEEE J. Solid-StateCircuits, vol. 45, no. 9, pp. 1896–1905.

- [5] Hazucha. P, Karnik. T, Bloechel. B. A, Parsons. C, Finan. D, and Borkar. S, (2005), "Area-efficient linear regulator with ultrafast load regulation," IEEE J. Solid-State Circuits, vol. 40, no. 4, pp. 933–940.

- [6] Ingino. J. M and Kaenel. V. R. V, (2001), "A 4-GHz clock system for a high performance system-on-achip design," IEEE J. Solid-State Circuits, vol. 36, no. 11, pp. 1693–1698.

- [7] Jakushokas. R, Popovich. M, Mezhiba. A. V, Kose. S, and Friedman. E. G, (2011), Power Distribution Networks with On-Chip Decoupling Capacitors, 2nd ed. New York: Springer-Verlag.s

- [8] Kim. J, Lee. W, Shim. Y, Shim. J, Kim. K, Pak. J. S, and Kim.J, (2010), "Chip package hierarchical power distribution network modeling and analysis based on a segmentation method," IEEE Trans. Adv. Packag., vol. 33, no. 3, pp. 647–659.

- [9] Kose. S and Friedman. E. G, (2010), "On-chip point-of-load voltage regulator for distributed power supplies," in Proc. ACM Great Lakes Symp. VLSI, pp. 377–380.

- [10] Kose. S and Friedman. E. G, (2011), "Distributed power network co-design with on-chip power supplies and decoupling capacitors," in Proc. Workshop Syst. Level Interconn. Predict., San Diego, CA, pp. 1–5.

- [11] Kose. S, Tam.S, Pinzon.S, Mcdermott. B, and Friedman. E. G, (2012), "An area efficient on-chip hybrid voltage regulator," in Proc. IEEE Int. Symp. Quality Electron. Design, pp. 2718–2721.

- [12] Kursun. V, Narendra. S.G, De.V.K, and Friedman. E. G, (2003), "Analysis of buck converters for onchip integration with a dual supply voltage microprocessor," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol.11, no. 3, pp. 514–522.

- [13] Le. H. P, Seeman. M, Sanders. S. R, Sathe. S, Naffziger. S, and Alon. E, (2010), "A 32 nm fully integrated reconfigurable switched-capacitor DC-DC converter delivering 0.55 W/mm2 at 81% efficiency," in Proc. IEEE Int. Solid-State Circuits Conf.,pp. 210–211.

- [14] Man. T. Y, Mok. P. K.T, and Chan. M, (2007), "A high slew-rate push-pull output amplifier for lowquiescent current low-dropout regulators with transient-response improvement," IEEE Trans. Circuits Syst. II, Exp.Briefs, vol. 54, no. 9, pp. 755– 759.

- [15] Or. P. Y and Leung. K. N, (2010), "An output-capacitorless low-dropout regulator with direct voltage-spike detection," IEEE J. Solid-State Circuits, vol. 45, no. 2, pp. 458–466.

- [16] P. R. Sallen and E. L. Key, "A practical method for designing RC active filter," IRE Trans. Circuit Theory, vol. 2, pp. 74–85, Mar. 1955.

- [17] Rincon-Mora. G. A and Allen. P. E, (1998), "Optimized frequency-shaping circuit topologies for LDOs," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 45, no. 6, pp. 703–708.

- [18] Zeng. Z, Ye. X, Feng.Z, and Li. P, (2010), "Tradeoff analysis and optimization of power delivery networks with on-chip voltage regulation," in Proc. IEEE/ACM Design Autom. Conf., Anaheim, CA, pp. 831–836.

- [19] Zhou. Q, Shi. J, Liu. B, and Cai. Y, (2011), "Floorplanning considering IR drop in multiple supply voltages island designs," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 19, no. 4, pp. 638–646.

- [20] Swartz.C.R (2012),"High performance ZVS buck regulator removes Barriers to increased power throughput in wide input range point-of-load applications", vicor corporation.